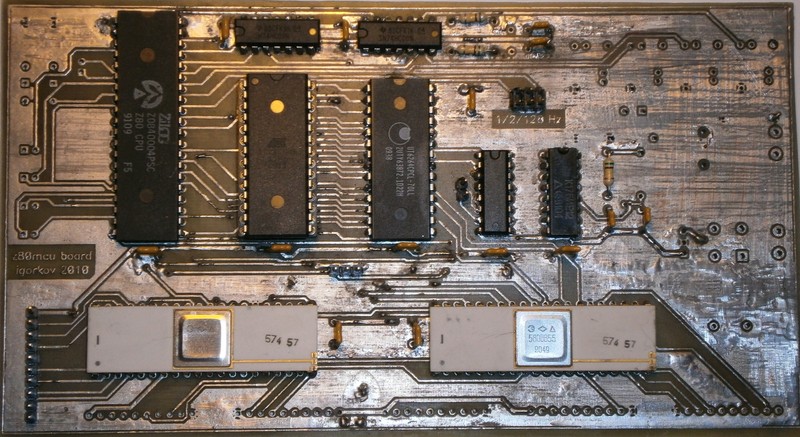

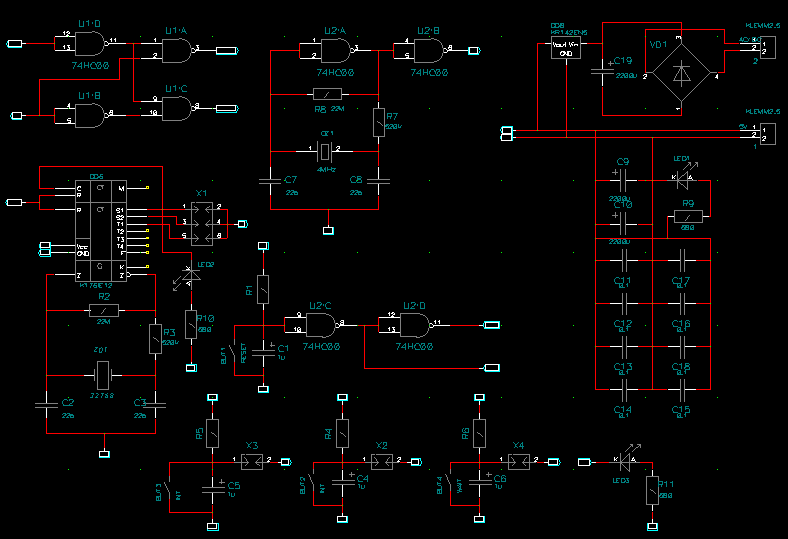

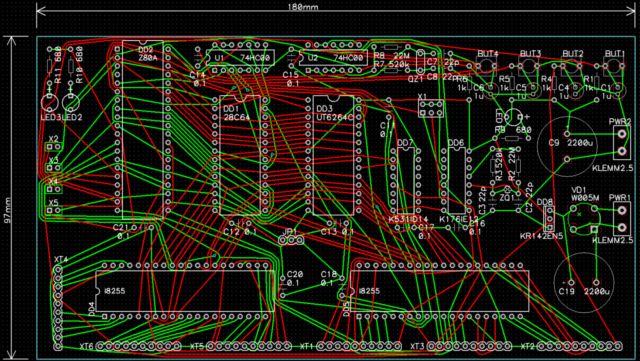

Рисунок 1 - Схема цифровых узлов

Вперед, в прошлое!

Хочу предложить Вашему вниманию интегрированный контроллер для различных применений. Сделан он на основе очень старого 8-битного микропроцессора Zilog Z80. Целью было собрать плату с архитектурой и элементной базой близкой к микрокомпьютеру 80ых. Цели у данного мероприятия в современном мире нет никакой, просто хотелось понастольгировать и собрать устройство на крупных компонентах, в DIP-корпусах, получить реально большой и работающий девайс, который можно пощупать "внутри" осциллографом и мультиметром (а не только отладчиком) и который будет наглядно отражать архитектуру компьютерной системы. В заключение попрограммировать под ядро i8080/Z80 на ассемблере.

Процессор Z80:

При разработке я пошел на некоторые упрощения, к примеру, использовал статическую память RAM одним чипом, а не целую горсть динамической, которая обычно устанавливалась в то время, в качестве ПЗУ стоит память EEPROM, в теории позволяющая перепрошить себя средствами самого процессора. В основе платы находится микропроцессор КР1858ВМ1, это отечественный клон легендарного Z80. Так же плата включает в себя 48 линий конфигурируемых портов ввода вывода, реализованных на 2х микросхемах К580ВВ55 (аналог i8255). Установлено 2 генератора: основной тактовый на 4МГц и вспомогательный, часовой, подключенный к линии прерываний.

Изначально очень хотелось сделать контроллер UART для данной платы, однако не нашел подходящих чипов для его реализации (К580ВВ51 требовал специфичного генератора К580ГФ24, плюс двойное питание, а все более современное показалось слишком сложным и "вычурным" на данной плате). Так же пришлось в целях упрощения отказаться от микросхем таймеров. Частично отсутсвие последних компенсируется часовым вспомогательным генератором.

Схема платы представлена на рис. 1 и 2. В ней все практически стандартно: процессор, память, порты ввода-вывода и вспомогательные цепи.

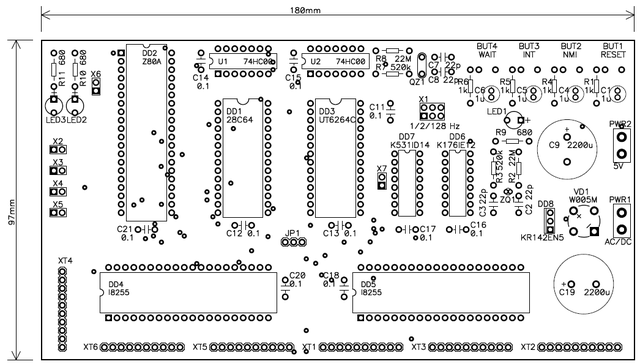

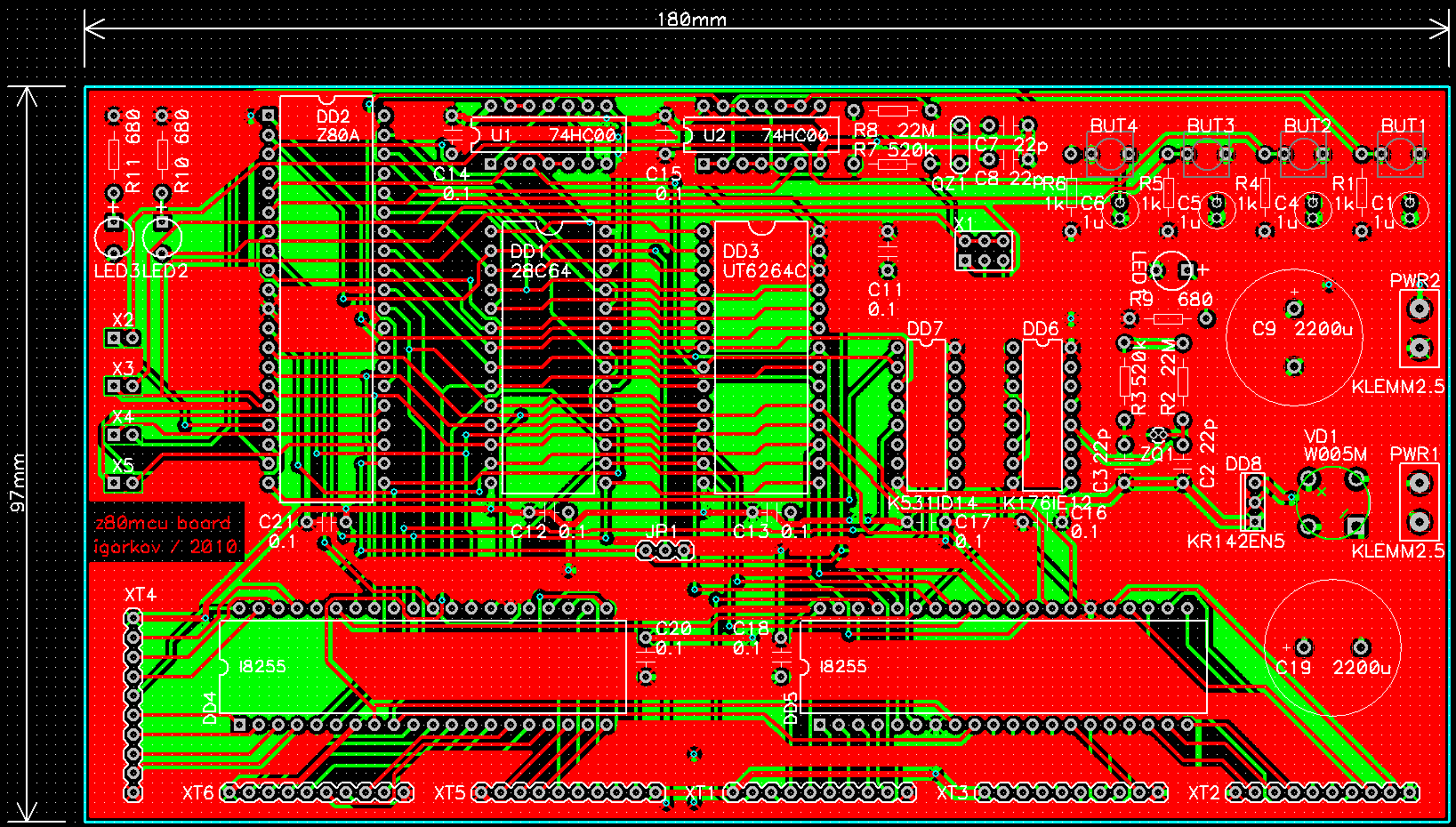

На рис. 3 представлена разводка платы в CAD-среде. Несмотря на упрощения и оптимизации, плата получилась довольно большой. Для меня, занимавшегося до этого разработкой устройств на SMD-компонентах, это был своеобразный рекорд по площади платы. Разводка производилась в Specctra с последующей ручной правкой.

В качестве эксперимента плата была так же разведена в топологическом трассировщике TopoR. Результат довольно забавный, однако, если присмотреться местами ужасный: некоторые дорожки делают чуть ли не полный оборот вокруг платы.

Так же через некоторое время после того, как выложил данный отчет в паблик, пришло письмо от ООО "Эремекс" с вторым вариантом разводки платы в ToPoR. Он представлен на рис. 6. Стараются ребята, за что им спасибо. Опять все такой же непривычный глазу вид, но качество разводки намного улучшилось. Возможно сказалось, что используется более новая версия. Так же был дан совет: выбирать из вариантов разводки тот что с 25мм/переход (на сколько помню, Топор после разводки предлагает несколько вариантов, вот из них и надо выбирать), в нем и получается меньше петель.

В сравнении с Спекктрой: 12 переходных у Топора, против 63 у Спекктры и на 1 метр меньше суммарная длина дорожек.

Плата 2х слойная, оптимизирована на изготовление и пайку в домашних условиях (сам использовал для этого ЛУТ). Установлена ширина сигнальных дорожек 0.45мм, а для линий питания и вовсе 0.8мм. Минимальные зазоры около 0.3мм. Так как в домашних условиях металлизацию отверстий провести практически невозможно (во всяком случае мне неизвестна ни одна доступная технология), при сборке требуется припаивать компоненты с 2х сторон платы, но данное требование не относится к компонентам, закрывающим плату, таких как конденсаторы, коннекторы питания и некоторые другие: у них принудительно сделано.

На плате предусмотрено несколько джамперов. Первый блок джамперов отвечает за подключение сигнала к порту прерывания. Можно выбрать частоту генерации прерываний: 1Гц, 2Гц, 128Гц, 1024Гц (или вовсе отказаться от них). Отдельным джампером подключается линия контроля записи к микросхеме ROM. Так же можно выбрать источник тактирования самого микропроцессора, к примеру установить тактирование от часовой микросхемы, что дает удобную отладку. В обычном режиме она не требуется, однако при подключении ее к пину записи процессора становится теоретически возможным перезаписать EEPROM средствами самого процессора.

На плате предусмотрены индикаторы:

И есть набор кнопок:

В топологии платы есть одна проблема, точнее проблема с корпусами компонентов: у советских микросхем шаг выводов 2.5мм, у зарубежных 0.1 дюйма, т.е. 2.54мм. На разводке платы я применил на всех корпусах шаг 2.54мм. С компонентами в DIP-40 это выливается в проблему установки. В принципе, ручная формовка выводов микросхем позволяет установить микросхему, но чтобы не иметь данную проблему, было бы хорошо найти оригинальный i8055 и Z80A, хотя на фотографиях можно увидеть, что вместо i8055 я смог поставить советский аналог К580ВВ55, пришлось, правда немного посидеть с плоскогубцами.

В таблице представлен полный список компонентов платы:

| Наименование | Количество (шт.) | Ориентировочная цена (руб.) |

| КР1858ВМ1 (Z80A, 80A, T34ВМ1) DIP-40 | 1 | 70.00 |

| КР580ВВ55 DIP-40 | 2 | 70.00 |

| К176ИЕ12, без аналогов (1990-97г) | 1 | 34.75 |

| SN74HC139N (КР1564ИД14) DIP-16 | 1 | 8.47 |

| SN74HC00N (КР1564ЛА3) DIP-16 | 2 | 11.60 |

| UT6264CPCL-70LL DIP-28-600 UTRON | 1 | 59.73 |

| AT28C64B-15PU DIP-28-600 ATMEL | 1 | 91.23 |

| L7805CV (+5В, 1.5А) TO-220 | 1 | 22.03 |

| TRL-28 DIP панель 28-контактная цанговая | 2 | 35.08 |

| TRL-40 DIP панель 40-контактная цанговая | 2 | 39.83 |

| TRS-16 DIP панель 16-контактная цанговая | 1 | 16.10 |

| PLS-40 штырьевой разъем, однорядный | 2 | 6.90 |

| PLD2-1 | 5 | 1.50 |

| PLD2-3 | 1 | 2.10 |

| КМ5Б М47 22пФ, 10% | 4 | 9.15 |

| КМ5Б Н90 0.1 мкФ | 11 | 12.71 |

| К50-35 имп. 3300 мкФ х 25В 105°C | 2 | 20.34 |

| К50-35 имп. 1 мкФ х 6.3-25В 105°C | 4 | 10.34 |

| С1-4 имп. 0.25 Вт, 5% 22 мОм | 2 | 2.88 |

| С1-4 имп. 0.25 Вт, 5% 510 кОм | 2 | 2.88 |

| С1-4 имп. 0.25 Вт, 5% 1.5 кОм | 4 | 2.88 |

| С1-4 имп. 0.25 Вт, 5% 680 Ом | 3 | 2.88 |

| FR4 100х200мм (1.5мм), стеклотекстолит | 1 | 64.41 |

| W005A диодный мост | 1 | 15.00 |

; Адреса портов ввода вывода: IO1_CONF: EQU 00h IO1_A: EQU 01h ORG 0x0000 LD A, 01h ; Конфигурирование ВВ55(1), OUT (IO1_CONF), A ; настройка PortA как выход. LD A, 01h ; Инициализируем порт. loop: OUT (IO1_A), A ; Вывод байта в порт. RLC A, 1 ; Циклический сдвиг влево. JP loop ; Бесконечный цикл. END

Для запуска примера требуется установить тактирование микропроцессора на 1-2Гц, так как в программе для простоты не сделаны необходимые задержки. В листинге 2 представлен вариант программы с работой через прерывание, для его работы должны быть поданы сигналы тактирования от 4Мгц и от часового генератора.

; Адреса портов ввода вывода: IO1_CONF: EQU 00h IO1_A: EQU 01h ORG 0x0000 reset: DI ; Запрет прерываний. LD SP, 08FFFh ; Настройка стека. LD A, 01h ; Конфигурирование ВВ55(1), OUT (IO1_CONF), A ; настройка PortA как выход. LD A, 01h ; Инициализируем порт. EI ; Разрешение прерываний. loop: JP loop ; Бесконечный цикл. ; Процедура обработки прерывания: DS 0x0038-$ ; Формируем смещение в бинарном образе. ORG 0x0038 ; int: OUT (IO1_A), A ; Вывод байта в порт. RLC A, 1 ; Циклический сдвиг влево. RETI ; Возврат из процедуры обработки прерываний. END

Для компиляции ассемблерных программ я использовал свободный компилятор ассемблера z80asm. Он распространяется в исходных кодах и без проблем собирается под Windows при помощи MinGW+msys.

Карта памяти для данных и портов ввода-вывода представлена в таблице 1. Можно только прокомментировать следующую особенность: в областях помеченных как Reserved на самом деле идет циклическое повторение предыдущих областей, так как старшие линии адреса просто не задействованы и их значения ингнорируются. Однако, логично не пользоваться данной особенностью.

Памяти программ установлено не много - всего 8кБ, а вот оперативной памяти не мало даже по меркам современных 8-битных микроконтроллеров ARV/PIC, те же 8кБ, хотя без переделок можно установить микросхему на 16кБ.

Адресное пространство ввода-вывода:

0x00-0x03 - ВВ55(1) 0x04-0x07 - ВВ55(2) 0x08-0xFF - reserved 0x0100-0xFFFF - reserved

Адресное пространство кода-данных:

0x0000-0x1FFF - ПЗУ (EEPROM) 0x2000-0x7FFF - Зарезервировано 0x8000-0x9FFF - ОЗУ (SRAM) 0x9000-0xFFFF - Зарезервировано

На каждую микросхему порта ввода-вывода приходится 4 адреса, они имеют следующие значения:

0x00, 0x04 - [Conf] Конфигурационный регистр порта ввода-вывода 0x01, 0x05 - [PortA] Регистр порта A 0x02, 0x06 - [PortB] Регистр порта B 0x03, 0x07 - [PortC] Регистр порта C

При этом регистр конфигурации имеет следующий формат: (взять и DS).

Проверку функционирования платы можно разбить на следующие этапы:

После этого плату можно признать полностью функционирующей.

Стоит упомянуть, что при сборке я провел эксперимент с лужением сплавом Розе в кипятке. По этой причине плата полностью покрыта припоем.

Я при сборке не стал сразу распаивать плату полностью. Начал с цепей питания, проверил что все в порядке, распаял генераторы, проверил, что есть генерация, после этого впаял панельку под процессор и минимальные цепи обвязки. Здесь уже было посложнее, пришлось проверить осциллографом, происходит ли попытка выборки инструкции из внешней памяти. Когда убедился что все в порядке, распаял оставшиеся цепи обвязки процессора (кнопки и т.д.). После этого стал ставить память. Сначала ПЗУ, затем ОЗУ. После этого можно было попробовать работу ПЗУ и залить первую микропрограмму. Убедившись, что все в порядке, распаял все оставшиеся компоненты.

Итоговый вид собранной конструкции представлен на рис. 7. К сожалению, на фотографии плата в несколько подпорченном виде: с нее сняты некоторые комплектующие в цепях питания.